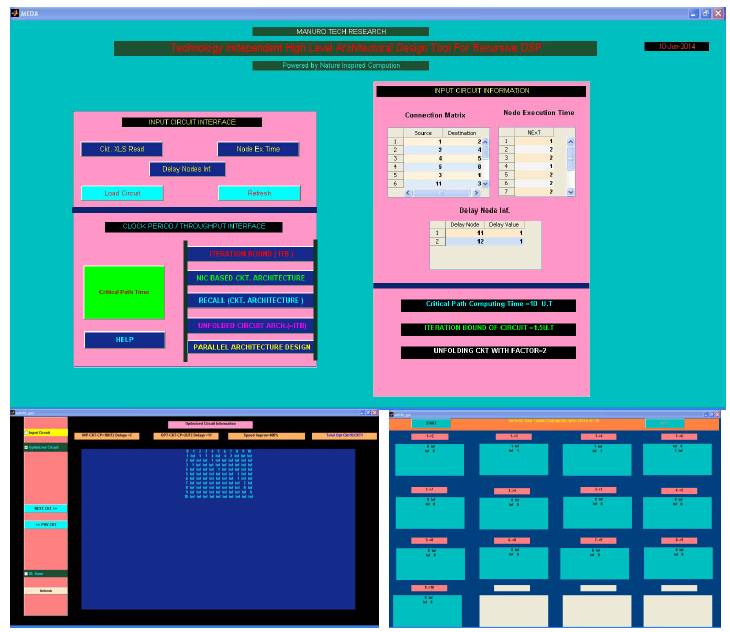

MEDA-TIHLA: Manuro EDA for Technology Independent High Level Architecture Design

The increasingly complicated embedded signal processing systems requires extensive design automation and optimization tools. One of the most challenging problems in high-level synthesis is how to explore a wide range of design options to achieve high-quality designs within a short time .In many applications the performance of a circuit dominates all other concerns. The performance of a synchronous circuit is measured using throughput, the rate at which the circuit completes computations, and execution time, the time it takes to perform a single computation from input to output. Many iterative or recursive applications of signal processing can be represented by data flow graphs, or DFGs. The nodes of a DFG represent tasks, while edges between nodes represent data dependencies among the tasks, either within iterations (an execution of all tasks) or between iterations. To model repeated steps within an algorithm, a DFG may contain loops. To meet the desired throughput or speed of the circuit which implement it, it is necessary to have an optimal circuit which could satisfy the objective. TIHLA is an EDA tool to design the optimal circuit at high level which deliver the best possible speed or satisfy customize requirement of speed. There are various facilities are available in MEDA-TIHLA like: Estimation of Critical path, Estimation of Iteration Bound, Customize speed based Automated Multiple circuit design, Design of circuit which may pose maximum value of speed in fraction form effectively, Development of Parallel architecture from serial architecture etc. A very user friendly environment has developed to enter the input circuit as connection matrix through XL sheets. Out put circuit performances are also available in terms of speed and number of delays involved in circuits with percentage improvement. A unique feature of this tool is to provide number of circuit design for same speed requirement with the help of NIC. This helps to satisfy the situation in demands in optimal manner.